disassembly - Why ther are some many padding/leading nop instructions in my binary code? - Reverse Engineering Stack Exchange

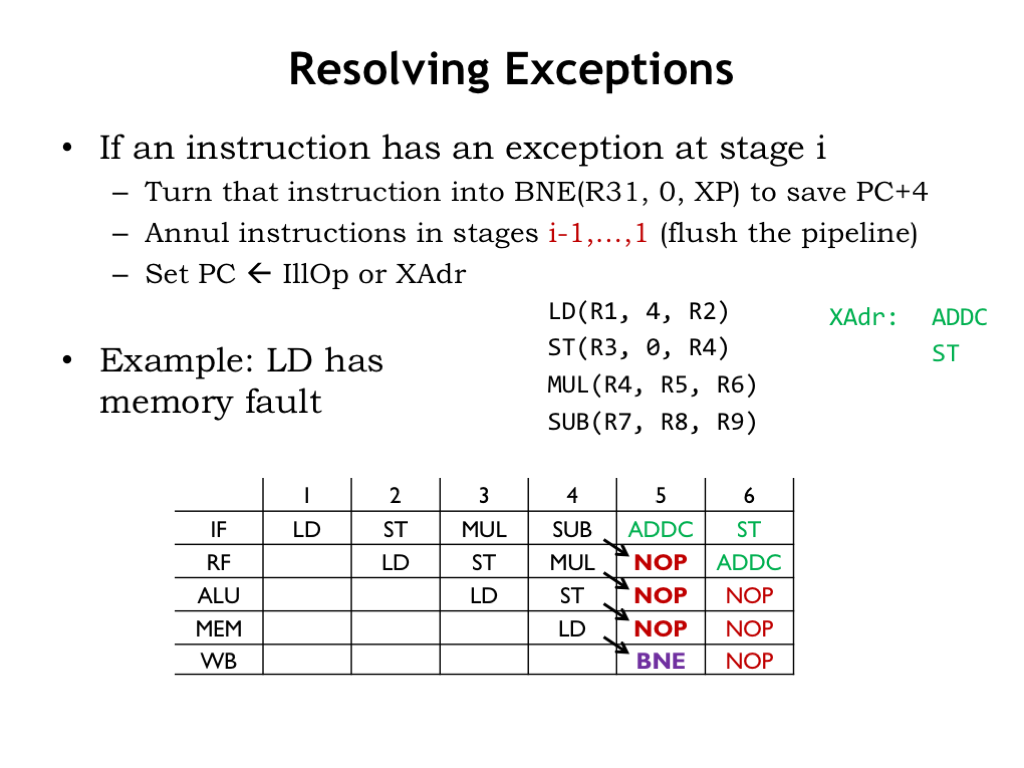

15.1 Annotated Slides | Computation Structures | Electrical Engineering and Computer Science | MIT OpenCourseWare

Execution of test instructions instead of NOP in PAYEH processor using... | Download Scientific Diagram

Timing of the scenario draw in Figure 3 as we add nop operations: a) 1... | Download Scientific Diagram

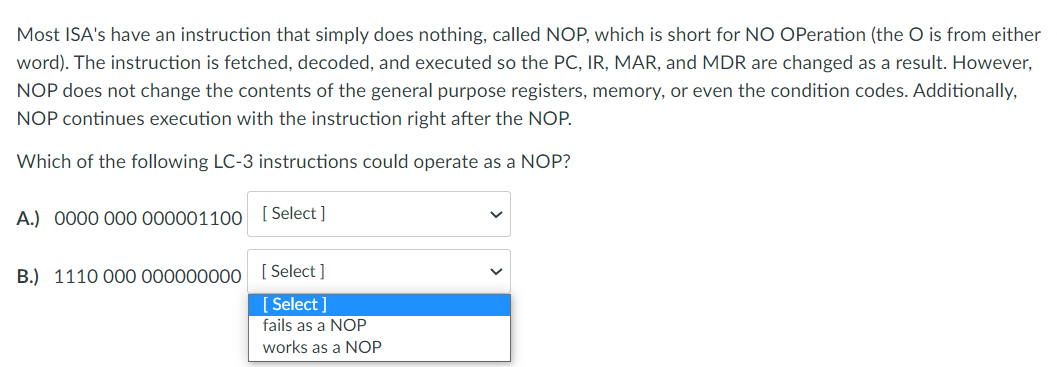

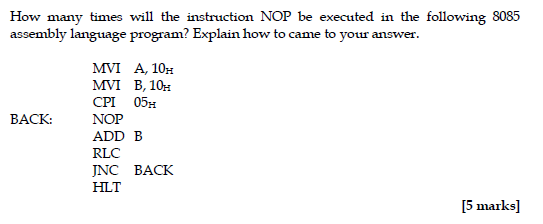

SOLVED: Most ISAs have an instruction that simply does nothing, called NOP, which is short for NO OPERATION (the O is from either word). The instruction is fetched, decoded, and executed so